Čas od času se hodí znát vnitřní strukturu naprogramovaného obvodu GAL nebo PAL. Bohužel, tyto obvody mají často zamčenou pojistku a tak se jednoduše přečíst nedají. Čtení pomocí Arduino bastlu a ruční analýzu pomocí Excelu už mám celkem zmáknutou, ale je to dřina. Proto mně celkem zaujal projekt DuPAL od Fabio Battaglia.

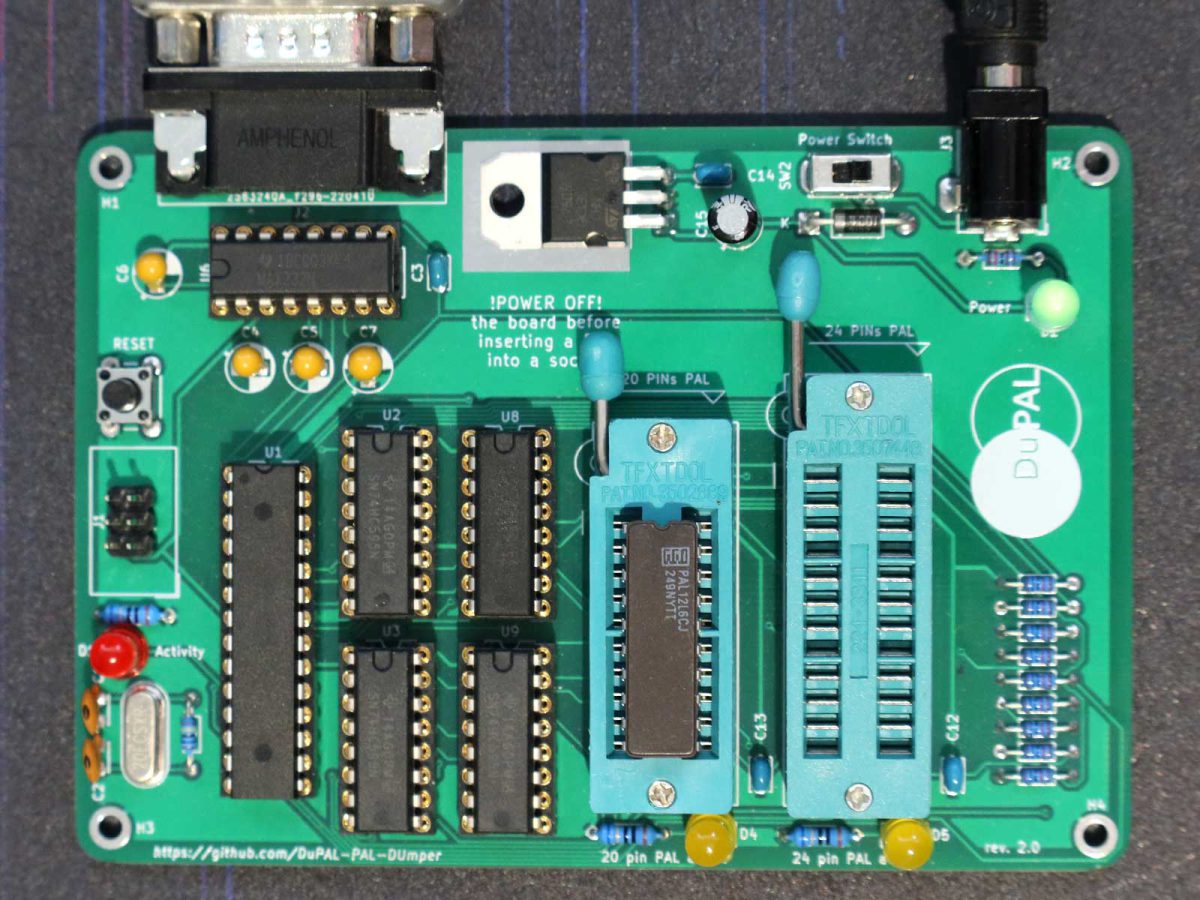

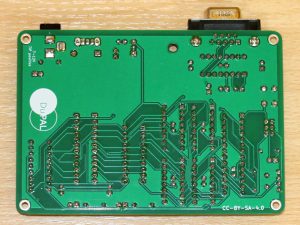

Projekt má svoji hardwarovou i softwarovou část. Hardware je poměrně jednoduchý. Je založený na oblíbeném „Arduino“ MPU ATmega328P, který doplňují tři sériově-paralelní a jeden paralelně-sériový převodník a obvod MAX232 pro RS-232 komunikaci. Napájení je běžným zdrojem 7-12V, na desce je 5V stabilizátor. Pro PAL obvody jsou na desce úzké ZIF patice 20 a 24 pinů.

Trochu atypický pro mně byl Optiboot bootloader, který jsem neznal, ale nic, co by se nedalo zvládnout. Přes bootloader pak už nahrajete vlastní firmware, který nedělá nic jiného, než že poslouchá příkazy ze sériové linky a umí nastavit piny a načíst výstupy z PAL obvodu. O zpracování dat se stará software na počítači. Předchozí firmware měl i nějaké vlastní zpracování, ale to bylo z nejnovější verze odstraněno a vše řeší software. Hardware umí, nebo se alespoň snaží, rozpoznat 3-stavové výstupy. Počítač komunikuje s DuPAL deskou po sériové lince rychlostí 57600 Bd a načítání nějaký čas zabere. Například PAL12L6 z řadiče FDC800 se načítá asi minutu a půl.

A to už se pomalu dostáváme k softwaru. Celý je napsán v Javě, takže je multiplatformní a s výjimkou nástroje DuPAL Peeper pracuje čistě v příkazové řádce.

DuPAL Analyzer

DuPAL Analyzer slouží k načtení celého PAL obvodu do JSON souboru. Pokouší se rozpoznat i vnitřní registry a analýza může trvat celkem dlouho, autor uvádí, že i hodiny. Vše je popsané na stránce DuPAL Analyzeru a na doprovodném dokumentu k analýze. Já jsem zkoušel zatím jen jednoduchý PAL12L6 z FDC800, který jsem načítal jako 12H6 (12L6 software nezná, ale liší se jen negovanými výstupy). Analýza se spouští příkazem:

java -jar analyzer.jar COM5 12H6 out.json 3F

COM5 je port, kde mám DuPAL board připojený, 12H6 je typ obvodu, out.json je výstupní soubor a 3F maska, která říká, že 6 pinů 13-18 jsou výstupy. Načtený soubor má 4096 stavů, což odpovídá 12 vstupům a jejich všem kombinacím.

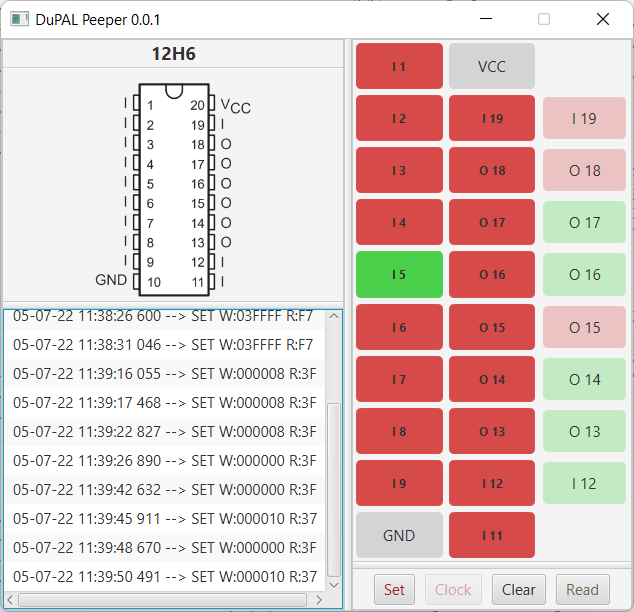

DuPAL Peeper

DuPAL Peeper je jediný nástroj s grafickým uživatelským rozhraním. Umožňuje „klikáním“ přepínat vstupy a vizuálně hned sledovat změny na výstupech. Spouští se jednoduše

java -jar peeper.jar --serial=com5 --pal=12H6

Zajímavou vlastností je, že Peeper umí fungovat buď přímo s PAL obvodem v DuPAL desce nebo v režimu simulace s načteným JSON souborem z Analyzeru. Můžete si tak později „hrát“ na počítači už bez připojeného hardwaru a podrobněji analyzovat funkci.

DuPAL Espresso Converter

Nástroj DuPAL Espresso Converter slouží pro konverzi ze souboru JSON, který vytvoří Analyzer do souboru, který umí načíst nástroj ESPRESSO logic minimizer. Spouští se příkazem

java -jar converter.jar FDC800_PAL12L6.json FDC800_PAL12L6.tab

a výsledkem je jedna nebo více tabulek (při více vnitřních stavech) pro nástroj ESPRESSO.

ESPRESSO logic minimizer

Nástroj původně vyvinutý IBM a posléze upravovaný mnoha autory, dnes již mrtvý a nevyvíjený, ale nepodařilo se mi za něj najít jinou rozumnou náhradu. Zajímavé jsou programy Logic Friday nebo Minilog, ale ty si vylámou zuby na velkých tabulkách. Program se spouští, stejně jako předchozí, z příkazové řádky

espr -o eqntott FDC800_PAL12L6_M.tab >FDC800_PAL12L6_M.EQN

Tentokrát jen není v JAVA, ale zkompiloval jsem C zdrojáky pro příkazovou řádku ve Windows. Parametr -o eqntott říká, že chci vygenerovat rovnice a ty jsou vytištěny na standardní výstup, odkud je přesměrovávám do souboru FDC800_PAL12L6_M.EQN.

Pro ověření jsem si vypálil PAL12L6 pro FD800 ze mnou původně vytvořených rovnic a s potěšením jsem kvitoval, že Analyzerem načtený JSON soubor je stejný jako na originálu zapůjčeném od Microlana. Mnou vytvořená rovnice má tento tvar

FDC = IORQ * A7 * A6 * /A5 * A4 * A3 * /A2

výstup z ESPRESSO vypadá takto

nFDC = (!A0&!A1&A2) | (nIORQ) | (!A7) | (!A6) | (A5) | (!A4) | (!A3) | (A0&A2) | (A1&A2);

rozdí je v tom, že můj výstup FDC je invertovaný v GAL společně s některými vstupními piny, takže pokud rovnici zinvertujeme (třeba v Logic Friday) a počítám s invertovanými některými vstupy, dostaneme už správný ekvivalentní tvar

FDC = A2' nIORQ' A7 A6 A5' A4 A3;

Zápis je trochu jiný, ale rovnice je stejná. Druhá možnost je použít pro ESPRESSO parametr -epos, který invertuje výstupy a tak dostaneme správnou rovnici rovnou, jen opět zapsanou s použitím trochu jiné syntaxe

FDC = (!A2&A3&A4&!A5&A6&A7&!nIORQ);

Obdobně vypadají i všechny další rovnice, které jsem původně napsal

; /DDEN=0 pokud /IORQ=0 a /WR=0 a v kombinaci s adresou DE (DE = 1101 1110)

DDEN = IORQ * WR * A7 * A6 * /A5 * A4 * A3 * A2 * A1 * /A0

nDDEN = (nWR) | (!A0&!A1&A2) | (nIORQ) | (!A7) | (!A6) | (A5) | (!A4) | (!A3) | (A0&A2) | (!A2);

invertováno DDEN = nWR' A0' A1 A2 nIORQ' A7 A6 A5' A4 A3;

-epos DDEN = (!A0&A1&A2&A3&A4&!A5&A6&A7&!nWR&!nIORQ);

; /WSID=0 pokud /IORQ=0 a /WR=0 a v kombinaci s adresou DD (DD = 1101 1101)

WSID = IORQ * WR * A7 * A6 * /A5 * A4 * A3 * A2 * /A1 * A0

nWSID = (nWR) | (!A0&!A1&A2) | (nIORQ) | (!A7) | (!A6) | (A5) | (!A4) | (!A3) | (A1&A2) | (!A2);invertováno WSID = nWR' A0 A1' A2 nIORQ' A7 A6 A5' A4 A3;

-epos WSID = (A0&!A1&A2&A3&A4&!A5&A6&A7&!nWR&!nIORQ);

; /RES=0 pokud MZ_RESET=1

RES = RESET

nRES = (!RESET);

-epos RES = (RESET);

; /DRIVE=0 pokud /IORQ=0 a /WR=0 a v kombinaci s adresou DC (DC = 1101 1100)

DRIV = IORQ * WR * A7 * A6 * /A5 * A4 * A3 * A2 * /A1 * /A0

nDRIVE = (nWR) | (nIORQ) | (!A7) | (!A6) | (A5) | (!A4) | (!A3) | (A0&A2) | (A1&A2) | (!A2);invertováno

-epos DRIVE = (!A0&!A1&A2&A3&A4&!A5&A6&A7&!nWR&!nIORQ);

; /BUS=0pokud /IORQ=0 a /RD=0 v kombinaci s adresami D8, D9, DA, DB (D8 = 1101 1000, DB = 1101 1011)

BUS = IORQ * RD * A7 * A6 * /A5 * A4 * A3 * /A2

nBUS = (nRD) | (!A0&!A1&A2) | (nIORQ) | (!A7) | (!A6) | (A5) | (!A4) | (!A3) | (A0&A2) | (A1&A2);invertováno

-epos BUS = (!A2&A3&A4&!A5&A6&A7&!nIORQ&!nRD);

Potěšilo mně, že se všechny rovnice shodují a příště tak už nebudu psát rovnice z hlavy, ale nechám si je pohodlně vygenerovat. Hlavně taky PAL12L6 ve FDC800 byl velmi jednoduchý příklad, kde jsou rovnice na první dobrou celkem dobře vidět a to je jen malá část PAL, se kterými se našinec potká. Příště to nemusí být tak jednoduché, tak je dobře na to mít nějaká nástroje.

Neviem, či je to to, čo hľadáš, ale ja na vygenerovanie logických rovníc z „pravdivostných tabuliek“ používam Simple Solver.

https://www.simplesolverlogic.com/download.html

Díky za tip, mrknu na to.

Jedna PCB doska by sa nenasla? Kupim 🙂

Ahoj, jasan, teda no, musim ji najit, ale nekde tu bude 😉 Posli mi pls adresu do e-mailu. Dik. Martin

Poslal som ti mail.