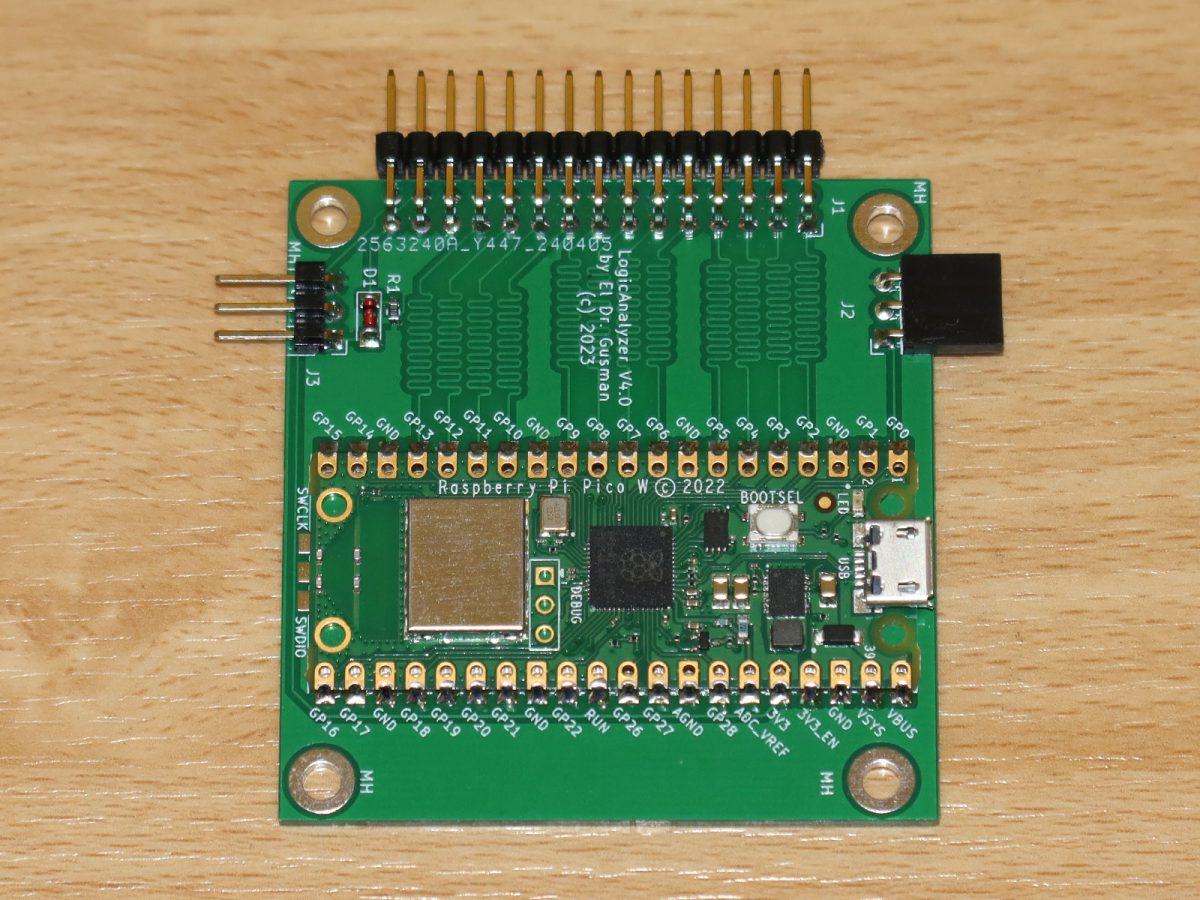

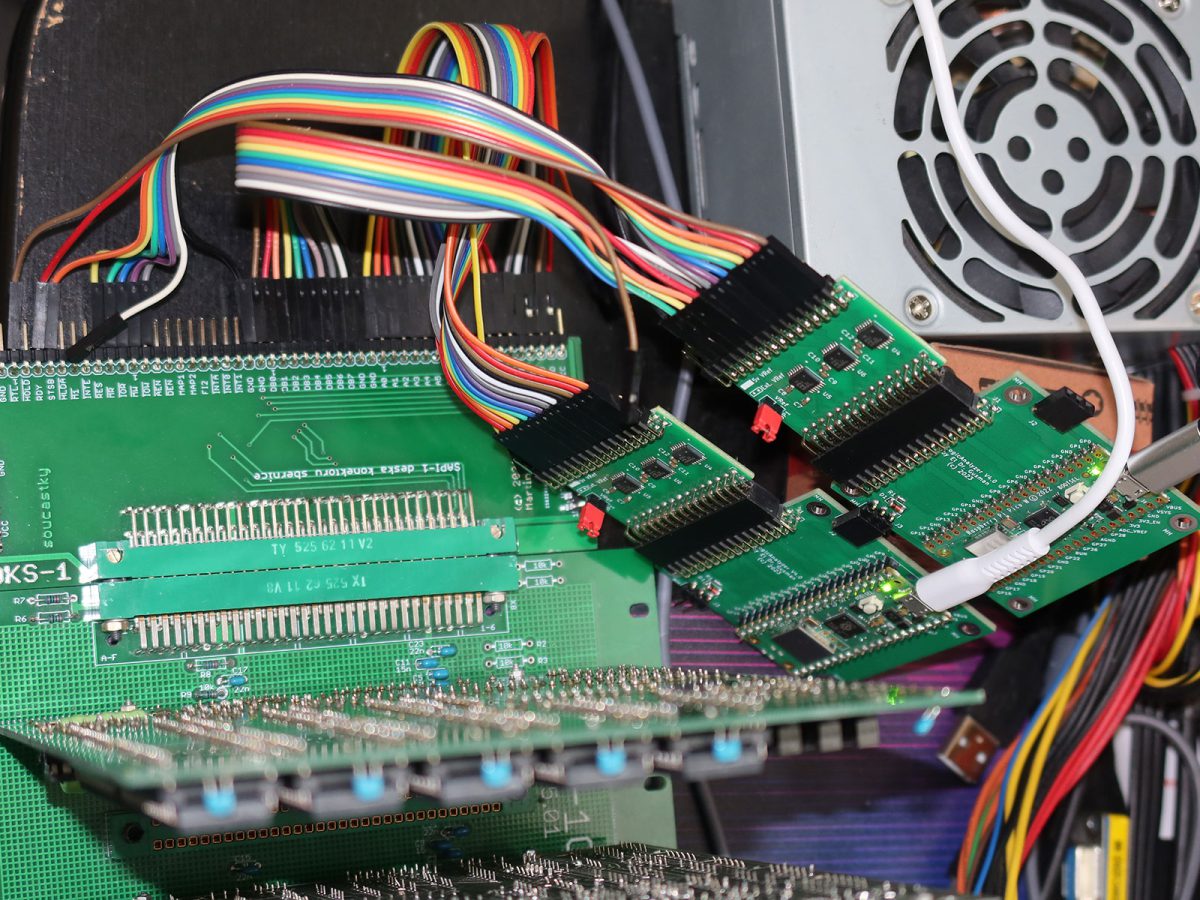

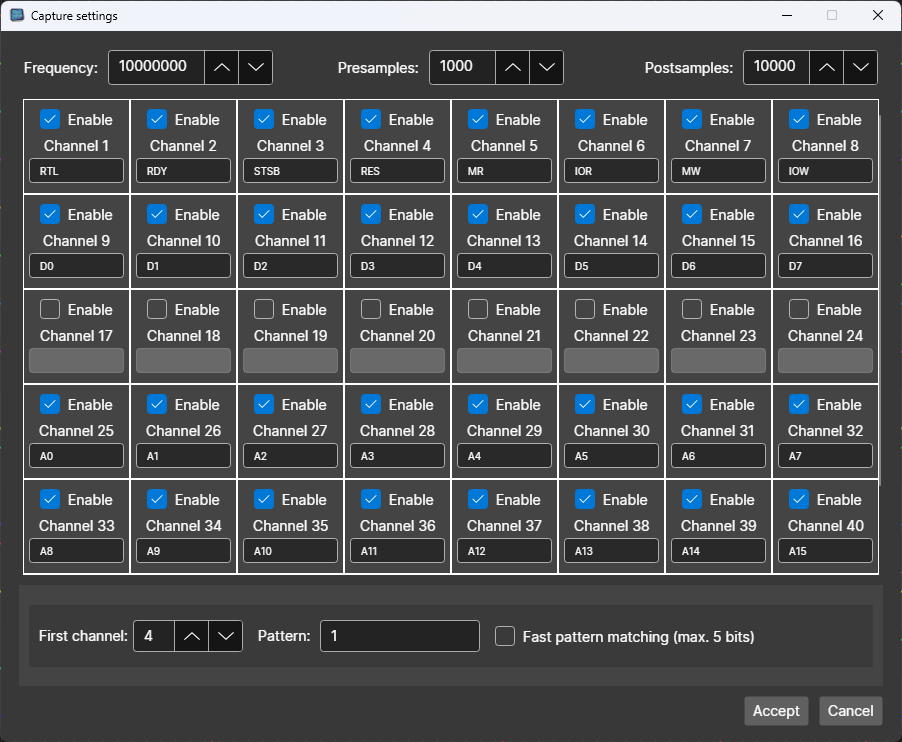

Projekt logického analyzátoru autora Agustín Gimenez Bernad má už skoro 2 roky. Postavil jsem si už jeho první verzi, ale teď s aktualizovaným hardwarem i softwarem začíná být opravdu zajímavý, zvláště pak pro použití na 8-bitech. Max. vzorkovací frekvence je 100 MHz, což je pro většinu mých projektů dostatečné. Základní část analyzátoru je v podstatě jen Raspberry Pi Pico s konektorem. Pro použití na běžných 8-bitech potřebujete ještě Level Shifter, který vám dovolí k Pico připojit 5V signály. Samotný analyzátor umí až 24 kanálů, což je samo o sobě celkem hodně, ale můžete vzájemně propojit až 5 analyzátorů a tím počet vstupů rozšířit na úctyhodných 120 kanálů. A nejlepší je, že to celé si můžete postavit sami za pár stovek.

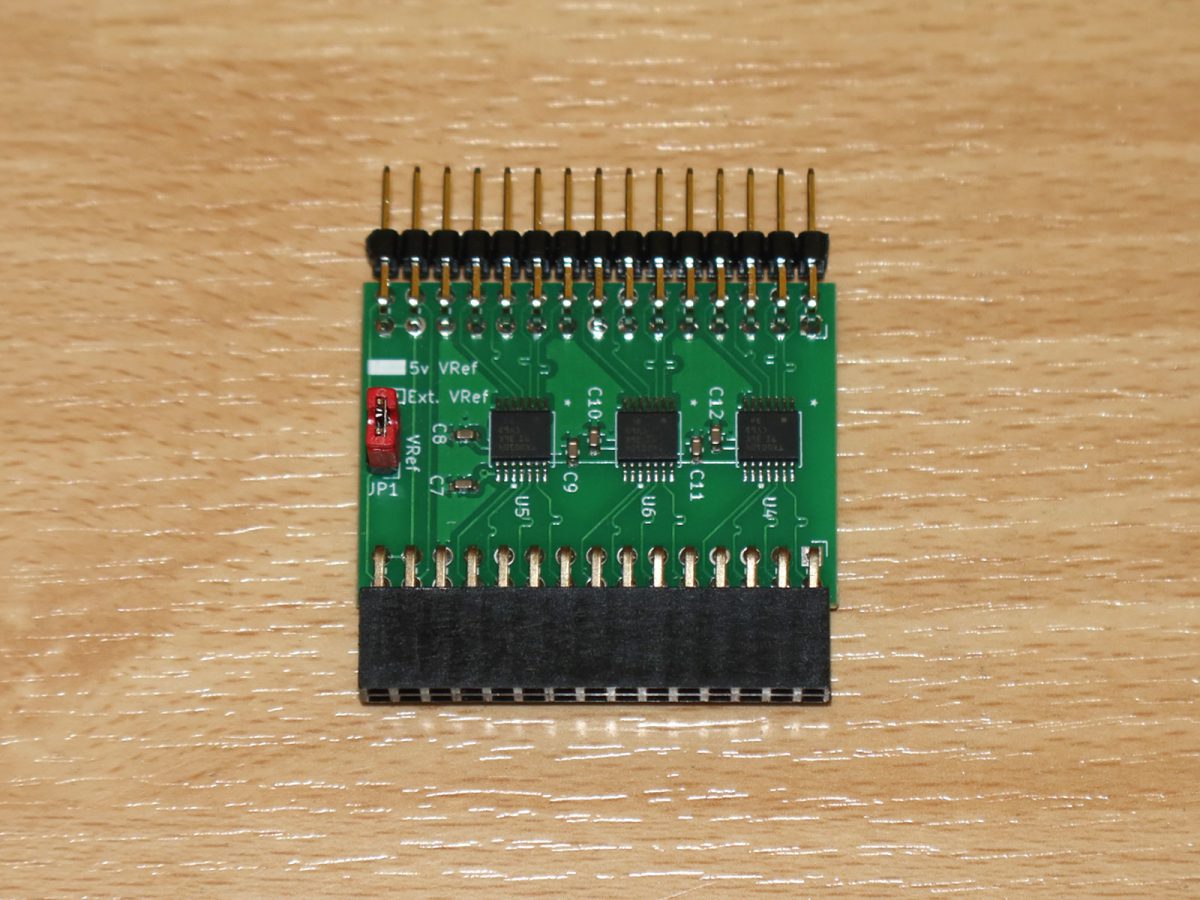

Celý projekt najdete na GitHub. Hardware je uložen jako zdrojové kódy v KiCAD, takže Gerbery si musíte udělat sami. Já jsem si vytvořil i soubory pro osazení a nechal 5 desek Level Shifteru rovnou osadit. Pokud chcete ušetřit, není nijak složité si 6 kousků TXU0104PWR a pár pasiv osadit sami, ale u mě vyhrála lenost 😉 Konektory už si musíte zapájet sami každopádně. Já jsem konektory osadil opačně než autor, přijde mi praktičtější mít na logickém analyzátoru samce. Má to stejně třeba i Saleae a jeho levné a hojně používané klony.

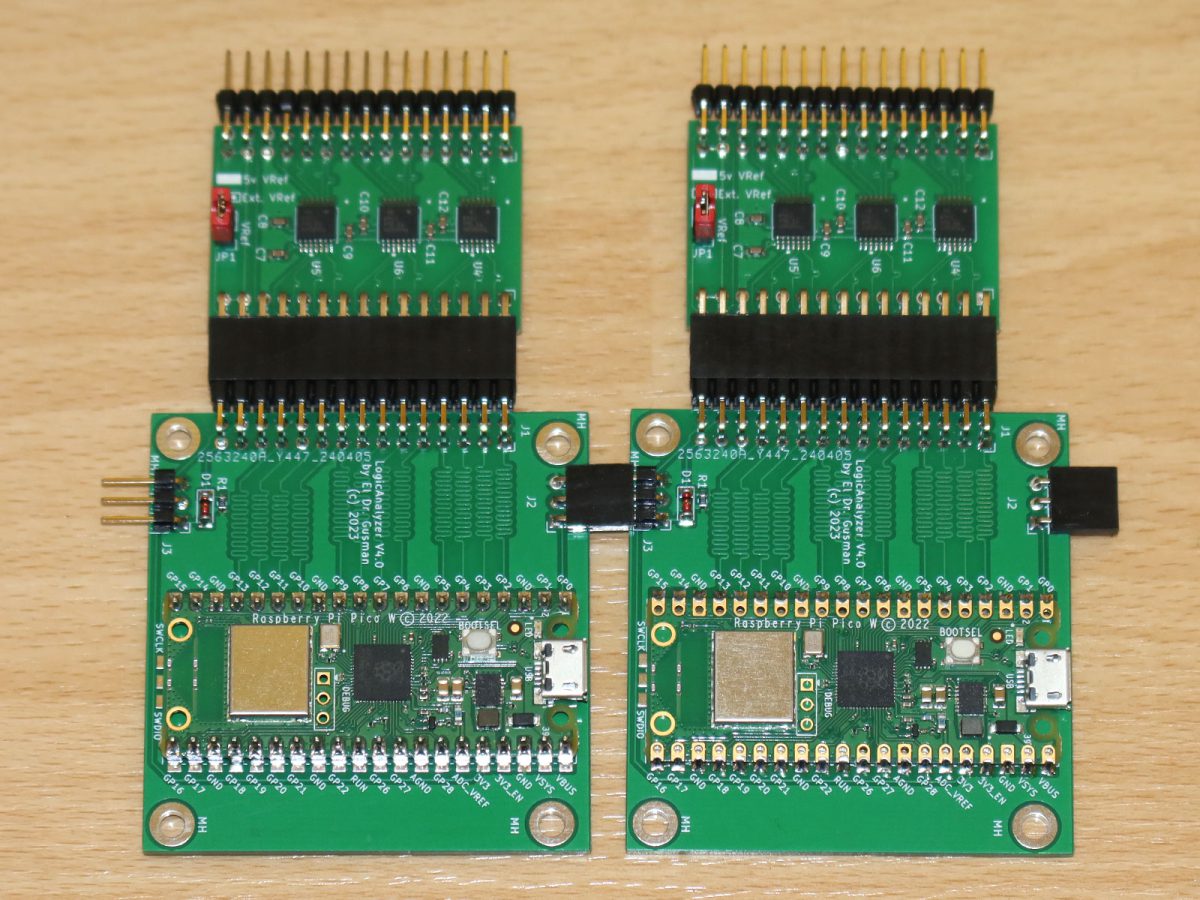

Raspberry Pi Pico jsem osadil ve WiFi verzi a jedno jsem dal přímo na desku, zatímco druhé jsem lehce přizvednul pinovou lištou. Je to proto, aby šel lépe zasunout microUSB konektor, když jsou dva analyzátory vedle sebe v Multidevice režimu. Při síťovém připojení se dá analyzátor napájet i přes připojovací konektor, ale člověk nikdy neví, USB je jistota.

Před pár dny se objevila na GitHub alternativní verze hardwaru, která má jen jednu desku a na ní přímo osazené diody a odpory na omezení napětí, takže se dá připojit jakýkoli signál mezi 3.3-5V. TXU0104 má zase jako výhodu Schmittovy klopné obvody na všech vstupech a dá se provozovat od 1.1 do 5.5V.

Software si autor píše vlastní. Myslím nejen firmware do Raspberry Pi Pico, ale i obslužný software analyzátoru. To je velká spousta práce a software zatím samozřejmě nemá funkce, které mají profesionální logické analyzátory, ale postupně funkcí přibývá. Hlavně analyzátorů různých komunikačních rozhraní a protokolů je zatím celkem málo. Ovládání je trochu zvláštní, prostě autorské, ale když se naučíte potřebné klávesy a klávesové zkratky je práce nakonec celkem pohodlná. Začátky ovšem byly trnité. Důrazně každému doporučuju přečíst si autorovu Logic Analyzer Wiki, kde je vše velmi pěkně zdokumentováno. A je toho hodně! Rozhodně doporučuji pročíst minimálně ovládání programu a část o triggerech a nejlépe všechno 😉 Jinak strávíte tápáním docela dost času, protože některé věci jsou prostě trochu jinak, než byste čekali.

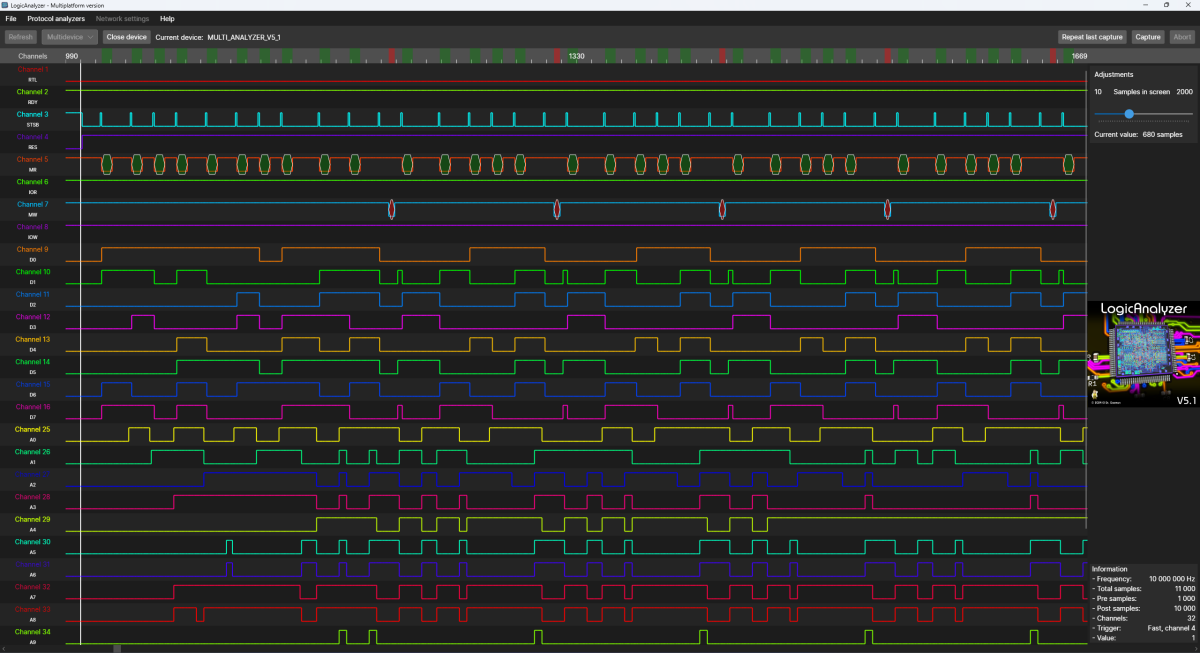

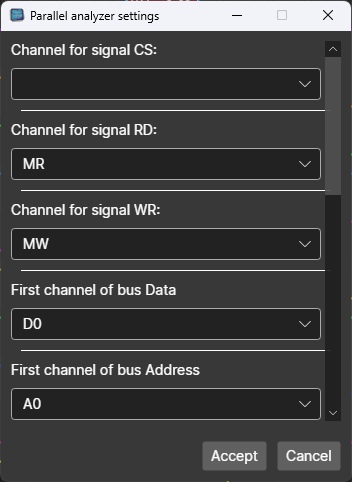

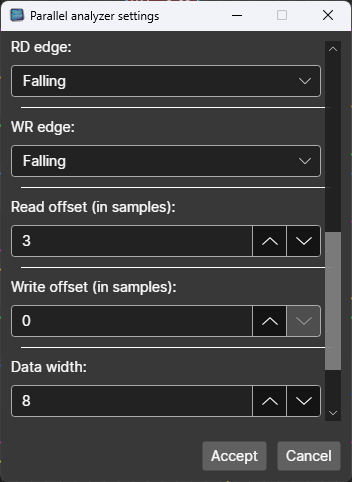

Autor navíc velmi pružně reaguje na jakékoli dotazy nebo požadavky a nedávno naimplementoval parallelní analyzátor sběrnice a vzal ho opět po svém, jak jsem v žádném analyzátoru zatím neviděl, ale velmi prakticky. Musíte zadat minimálně datovou sběrnici, lépe i adresovou a některé ze signálů CS, RD a WR, jejich hrany a zpoždění.

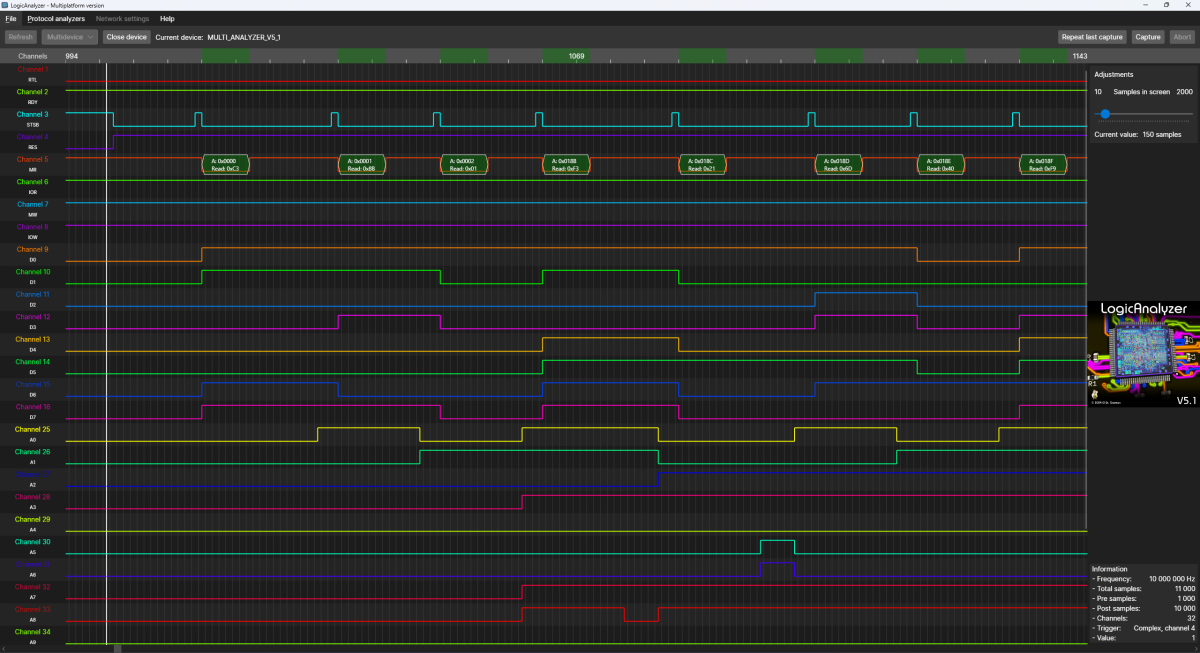

Po analýze vám tak analyzátor na příslušných signálech zobrazí hodnoty adresové a datové sběrnice. Během signálu RD se data objeví na sběrnici se zpožděním způsobeným přístupovou dobou pamětí. Na jiném analyzátoru jsem si pomáhal tím, že jsem data vzorkoval s nástupnou hranou signálu RD, ale tady se dá ponechat hrana sestupná a definovat zpoždění, např. při vzorkování 10 MHz zpoždění 3 vzorky je 300 ns, což je obvykle dostatečné.

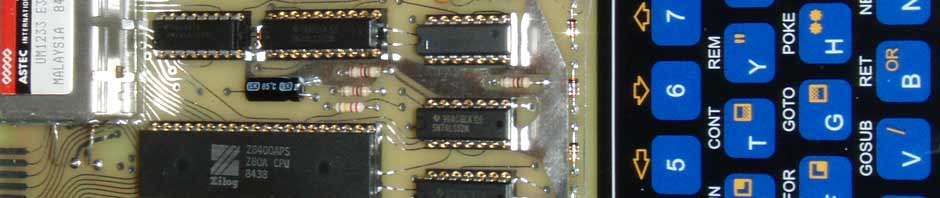

Analyzoval jsem například start počítače SAPI-1 v MIKOS, resp. MONITOR v5.0 a funguje to krásně.

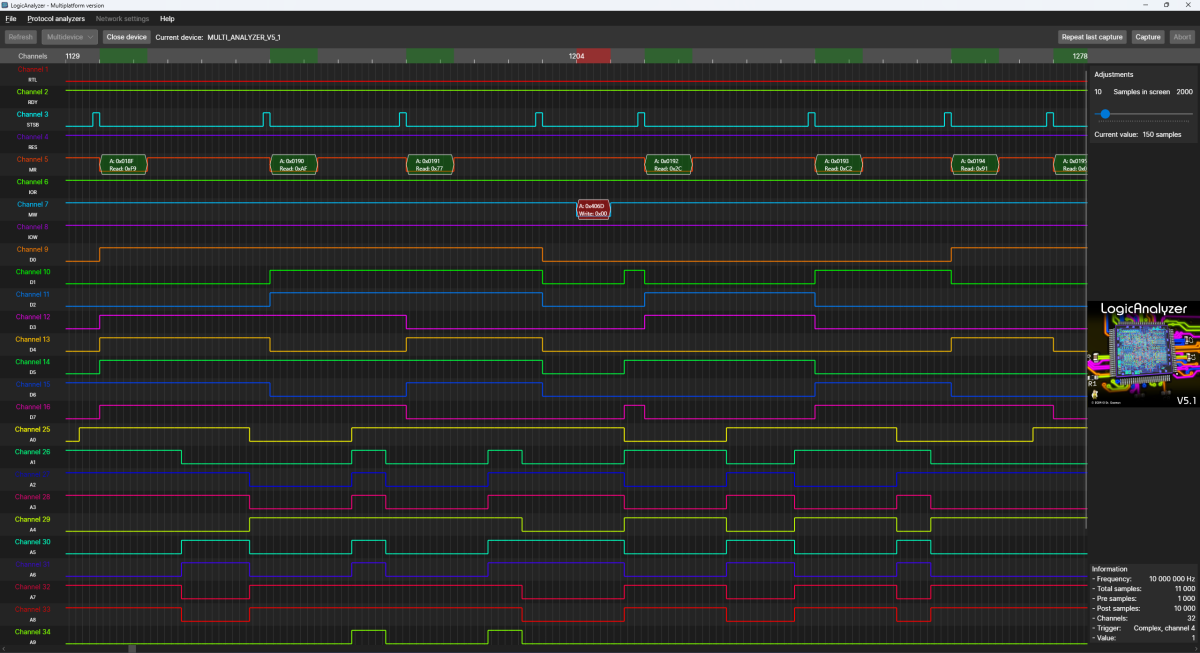

Pokud si obrázky zvětšíte, uvidíte, že program postupně prochází od adresy 0000 datové byty C3, 8B, 01, což je skok na 018B a opravdu adresa se následně mění na 018B a následuje hodnota F3, což je instrukce DI atd. po pár dalších instrukcích se objeví i zápis hodnoty 00 na adresu 40D6 a zápis se vždy po pár instrukcích opakuje. Zapsat by se to dalo třeba takto:

0000 C3 8B 01 JMP 018BH

018B F3 DI

018C 21 6D 40 LXI H,406DH

018F F9 SPHL

0190 AF XRA A

0191 77 MOV M,A

----> write 00 to addres 406DH

0192 2C INR L

0193 C2 91 01 JNZ 0191H

0191 77 MOV M,A

----> write 00 to addres 406EH

... smyčka pokračujeNo a když se mrknete na listing monitoru, uvidíte, že to tak opravdu je:

160 0000 C3 018B JMP COLD ; INICIALIZACE SYSTEMU

...

491 018B COLD:

492 018B F3 BEG: DI ; PRIKAZ "B"

493 018C 21 406D LXI HL,MSTAK ; NASTAV STACK POINTER

494 018F F9 SPHL

495 0190 AF XRA A

496 0191 77 BEG0: MOV M,A

497 0192 2C INR L

498 0193 C2 0191 JNZ BEG0 ; NULUJ M-RAMProgram prostě začíná tím, že zakáze přerušení, nastaví SP a vynuluje oblast proměnných monitoru na adresách 406D až 40FF.

Jo, když má člověk dost signálů na analýzu je to radost něco opravovat. Proto mi vždy vadily analyzátory, co mají jen 8 nebo 16 bitů, což je celkem obvyklé. No, „vadily“ je možná nesprávné až zlé slovo. Každá informace je dobrá, když člověk tápe, ale dostatek bitů je prostě super. A pokud si ten komfort můžete dopřát za dobré peníze, jděte do toho.

Velmi mile mě překvapila i synchronizace mezi analyzátory. Zkoušel jsem samplovat stejné signály na 100 MHz na obou propojených analyzátorech a byly na vzorek přesně stejně. To mě dost překvapilo. Autor posunutí detekuje a automaticky upravuje. Dle něj může vzniknout posuv +/-1 sample a i ten se dá manuálně posunout a opravit. Za mě to ale nebylo potřeba. Dobrá práce.

V plánu mám upravit moji desku konektoru sběrnice SAPI DKS-1, aby do ní šel analyzátor, resp. hned dva zapojit přímo a člověk, myšleno mé líné já, se nemusel zapojovat s kabely. To si raději nakreslím desku 😉

Pokud ta deska opravdu bude, a budou kousky navíc, hned se hlásím!

Za mě je to také zajímavý výrobek, především tou možností řetězení na více kanálů. Desku s tranzistorovými převodníky (je tam jen chvíli) už asi používat nebudu, protože mám tu původní a zdá se mi lepší. Asi to dám do společné krabičky (2x RPI, 2xpřevodník) tak, aby vznikla 48b. sestava. Za tu cenu je to, po hw stránce, naprosto perfektní.

Vzhledem k současným možnostem GU by mě lákalo použití v nějakém jiném sw, třeba PulseView. Už jste to někdo zkoušeli?

Super, když uděláš krabičku, hlásím se. Ta co tam je je jen na samotný L a ještě asi nějakou starší mez-verzi, protože mi nesedí, ani na ten první. Tranzistorovu verzi zkusím objednat, zase je fajn, že je to jedna deska.

Jestli smím prosit, kdyby byla nějaká hromadnější objednávka, dvě sady desek bych užil.

Pět kousků z JLCPCB je mi moc.

Je to měsíc zpátky, co jsem do jedné objednávky přihodil dvě Pi Pico :)) jen tak na dorovnání ceny :))) A jako když najdeš…

Ahoj Martine,

byla by jedna destička i pro Kláska do Bruntálu?

Díííky.

Mrknu, poslu e-mail.

zito: pokud by stačila ta původní ‚dvoudeska‘, tak mám i s těmi převodníky. Máš to ‚co by kamenem dohodil‘, tak se ozvi 😉

Už mu to dnes posílám 🙂

Jasně Michale, stavím se při příznivější hvězdné konstelaci. Předem napíšu.

Zbyla jeste jedna deska? Nebo uz jsem pozde?

Ahoj, ja uz bohuzel zadnou volnou nemam.

Analyzator super, jak jsem psal, hlavne moznost retezit jich vice 24-48-72. Ovsem nejvetsi slabinou je sw. Libilo by se mi propojeni do PulseView, kde je sw mnohem vice propracovany. Nasel jsem, ze uz se tim nekdo zabyval (https://forum.buspirate.com/t/logic-analyzer-development/86/2), ale ja sam jeste ne. Uz jste to nekdo zkousel? Asi bych byl rad, kdyby k teto uprave fw byly take zdrojaky.

To krupkaj: Mel bych jednu dvojici desek volnou. Je to pro ‚dvoudeskovou‘ variantu a sadu io pro interface. Ja jsem si je nedaval vyrobit s osazenim, ale jen hole plsp 😉

Hlásím se k zájemcům o desku do SAPI 🙂

Dnes jsem si s tím hrál a jako velkou slabinu vidím příliš malou paměť pro samply a pouze zjednodušený trigger který nechodí na hrany ale pouze stavy signálu. Proč je vlastně omezené samplování na 131071 samplů při snímání 1 – 8 kanálů když procesor má paměti více a navíc by při snímání například I2C na dvou kanálech šlo potřebu paměti ještě zredukovat? Obvykle pracuji s Picoscopem a i když cena je diametrálně rozdílná tak bych se ve vývoji SW inspiroval tam. Také se mi SW zaseknul. Samozřejmě uznávám že za tu cenu je muziky dost ale prostor pro zlepšení je také.

Ještě jsem testoval prográmek na který odkazuje Mikes21. Ve zkratce musím smeknout. S nějakou neoficiální verzí PulseView která podporuje Raspbery Pi Pico se dá s rychlostí až 120Msps snímat 24 kanálů digitálně a přitom použít větší část paměti na ukládání hodnot něž ve výše zmíněném projektu. Navíc jsou k dispozici 3 kanály analogové, ty se dělí pouze o 500ksps ale jdou namíchat analogové i digitální kanály současně. V projektu je tabulka která ukazuje že pokud se budou snímat pouze 4 kanály digitálně vejde se do paměti až 400k samplů. Ještě to má trochu chyby, protože se mi to také seklo s nějakým prázdným chybovým hlášením ale byl jsem navzdory tomu co tvrdí tabulka možností schopen s frekvencí 1.25Msps sejmout 500k samplů I2C komunikace (zřejmě stíhá odeslat některé záznamy do PC ještě než je přepíše novými). Pouze pokud natáhnu počet samplů na nesmyslně velkou hodnotu (třeba 10Ms) tak se začnou záznamy opakovat. Do budoucna je slíbená oficiální podpora v PulseView takže se moc těším. V kombinaci s tím co umí PulseView je to prostě bomba v poměru cena/schopnosti. Jen jsme asi přišli v tomto projektu o možnost jednoduše zřetězit Pika do sebe (kdo hledá nějakou cestu najde :-)).

Pingback: Ještě jednodušší alternativa logického analyzátoru | Martinův 8-bitový blog

Pingback: Připojení logického analyzátoru ke sběrnici SAPI-1 | Martinův 8-bitový blog

Vypada to, ze vyuziti noveho RPi Pico 2 narazilo na nejaky problem s GPIO. Podle Errata to vypada na chybu v hw noveho SoC. Gusman uz na to prisel: https://github.com/gusmanb/logicanalyzer. Skoda, LA mohl ziskat treba vice pameti a taky i rychlost.

Dobrá zpráva, Gusman vzal Pico 2 na milost 😉 a ještě se připravuje nová verze sw i fw. Koukal jsem na náhled a vypadá to, že tam udělal opravdu velký kus práce. Zároveň jsou importované analytické pluginy z PulseView. IMHO to tím získává mnohem vyšší úroveň.

Další bonus je, že by to mohlo podporovat mnohem vyšší kmitočet, určitě 200MHz a možná i více. To je až neuvěřitelné, co se s těmi malými SoC dá dělat.

Akorát s tou širší deskou se musí všechno předělat 😉 Asi za mně to budu po očku sledovat a uvidíme kam se dostane, zatím bych se nepouštěl do větších akcí. Na SAPI je už stávající verze dost overkill 😉 Zajímavý by bylo RP2350B a dát hot přímo na desku. Ale to je zase víc práce 😉

ahoj

muzu poprosit o jednu desku DKS-1A + desku logickeho analyzatoru?

dik

v

Vyderzaj pinoner 😉 E-mail mam, prosim chvili o strpeni, musim pohledat a mam toho moc. Desku DKS-1A jeste jednu mam, ten LA by tu taky mel byt, ale to neni s jistotou. Ozvu se.